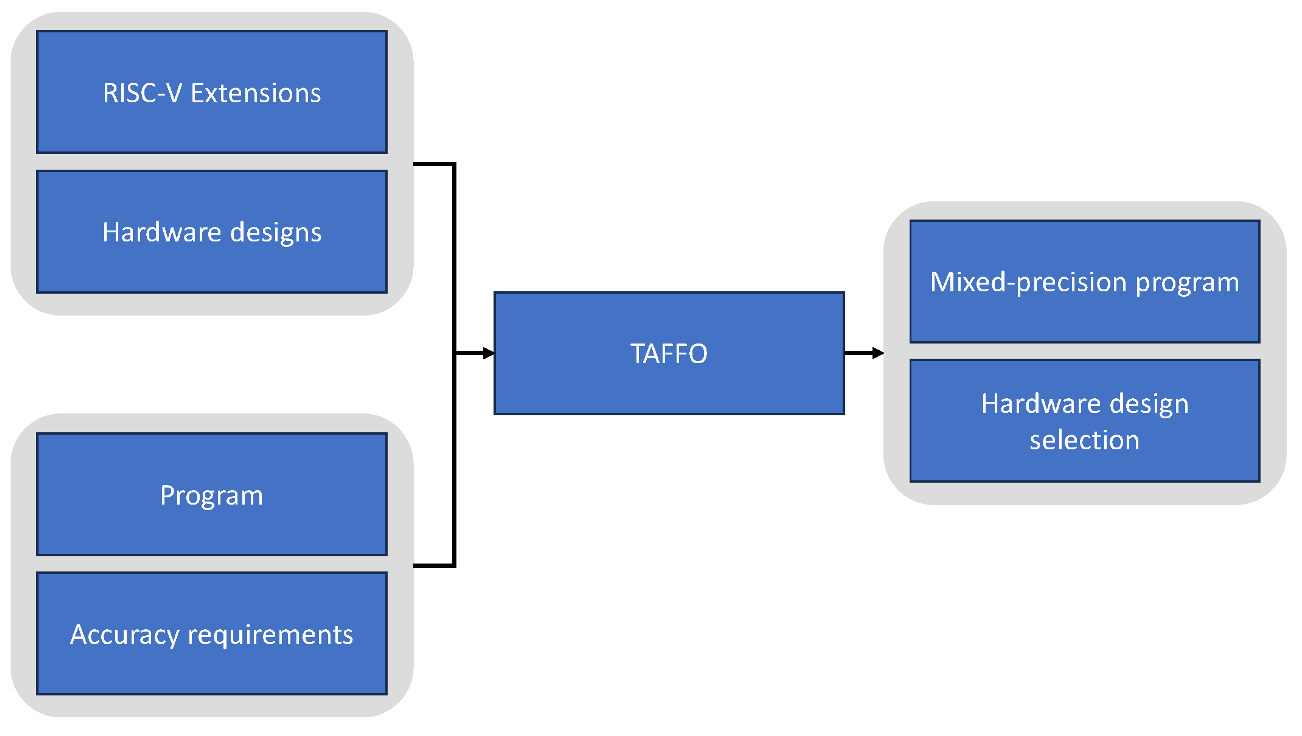

Mixed-precision is an approximate computing technique that allows to trade-off computation accuracy for speedup or energy efficiency. The effectiveness of mixed-precision depends on both software and hardware implementation, which calls for a software-hardware co-design approach based on the characteristics of the application. This paper describes the necessary evolution of hardware designs and compiler-based precision support. We describe the mixed-precision RISC-V-based FPUs as well as fixed-point support at the hardware and architecture level that would benefit the programs in mixed-precision. Then we describe the changes in the LLVM-based precision-tuning compiler framework TAFFO that need to be implemented to take advantage of the hardware architecture changes.

We conclude with the prospect of compiler that based on the accuracy requirements provided by the programmer can generate both mixed-precision version of the program and select the optimal hardware platform for its execution.

We conclude with the prospect of compiler that based on the accuracy requirements provided by the programmer can generate both mixed-precision version of the program and select the optimal hardware platform for its execution.

The paper is available at: https://zenodo.org/record/8101155

At at IEEE website: https://ieeexplore.ieee.org/abstract/document/10137092